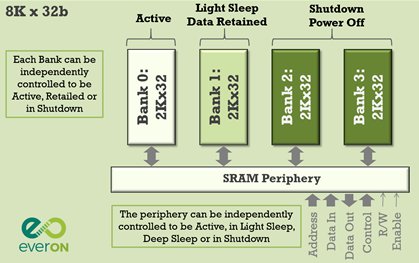

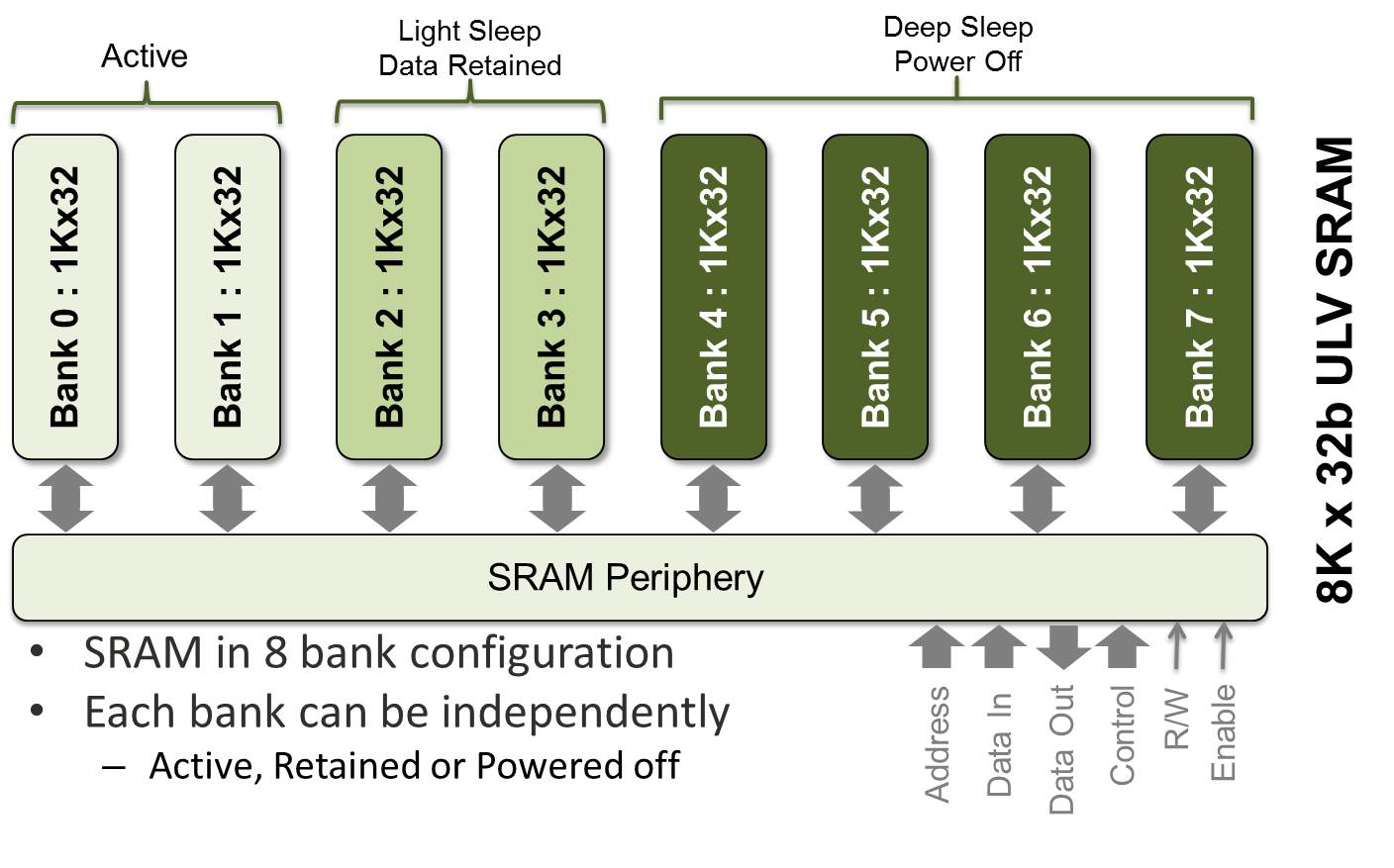

US8370557B2 - Pseudo dual-port SRAM and a shared memory switch using multiple memory banks and a sideband memory - Google Patents

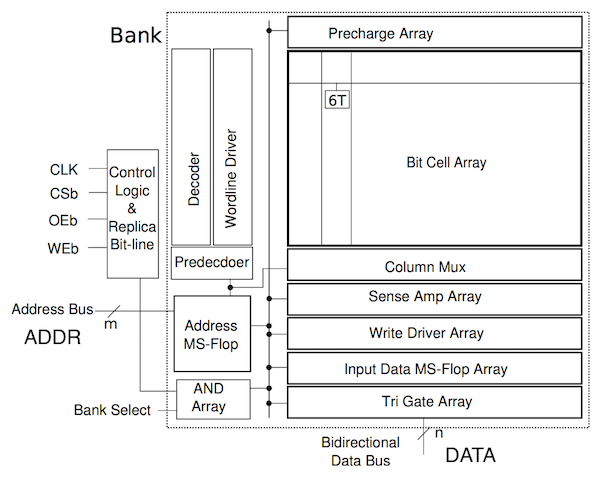

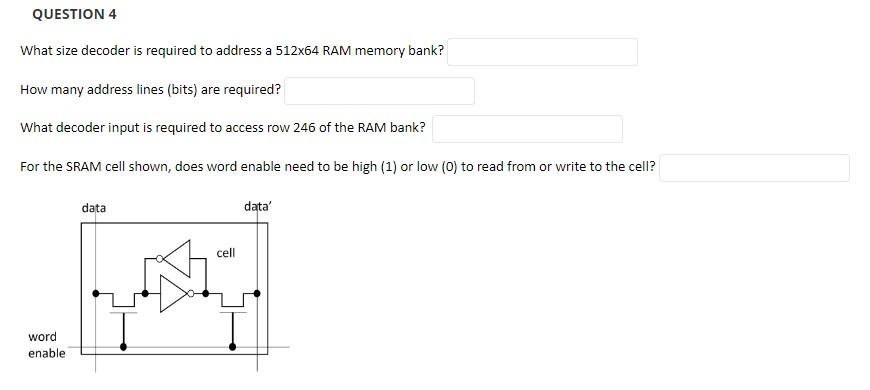

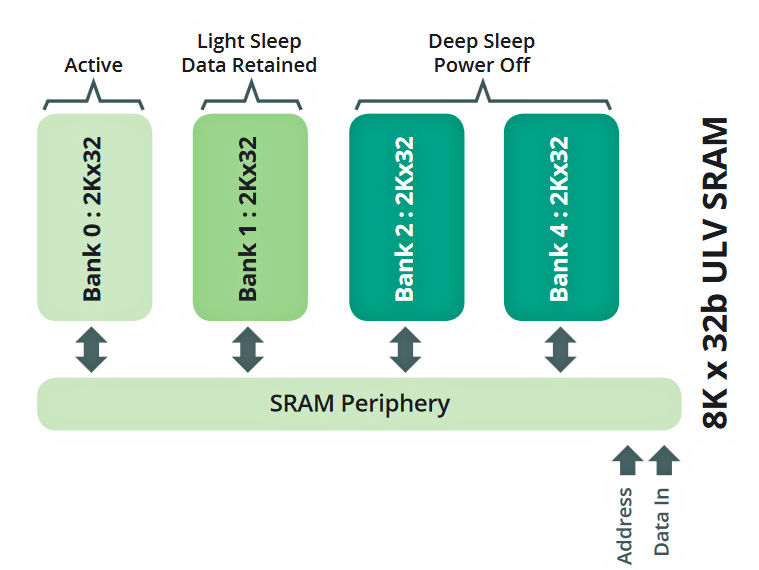

Figure 18 from Single-Ended Subthreshold SRAM With Asymmetrical Write/Read-Assist | Semantic Scholar

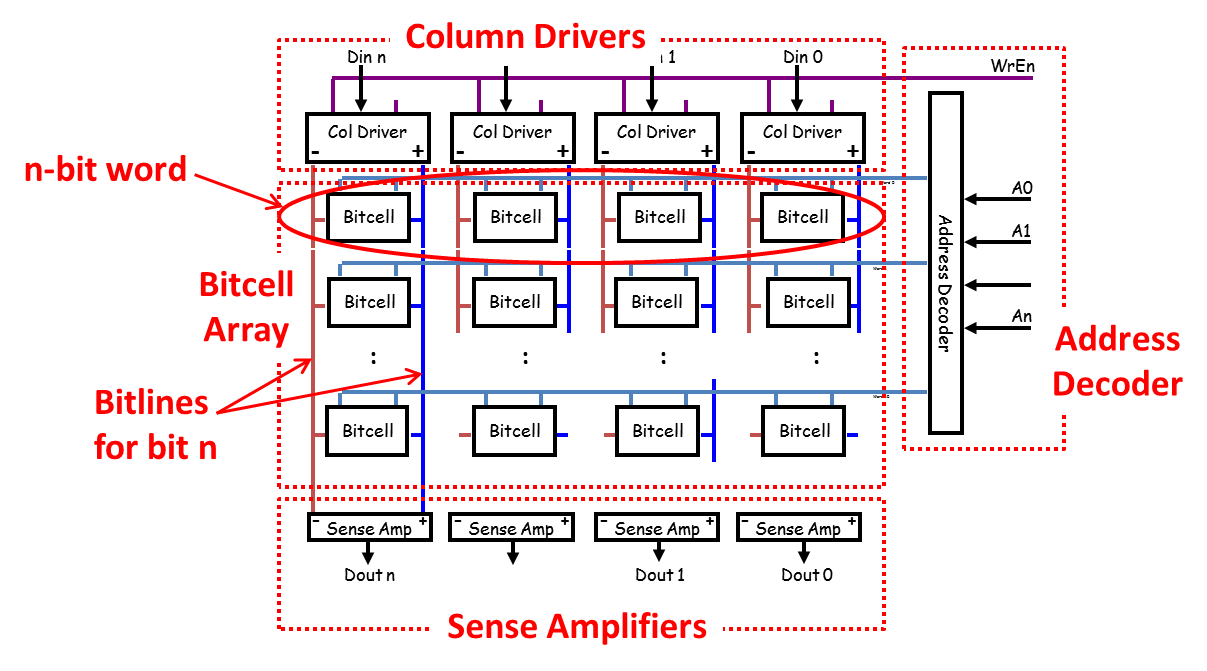

Figure 5 from A 0.6-Tbps, 16-port SRAM design with 2-stage- pipeline and multi-stage-sensing scheme | Semantic Scholar

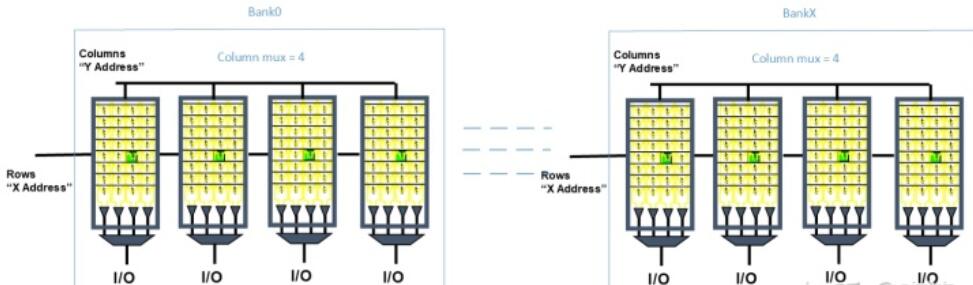

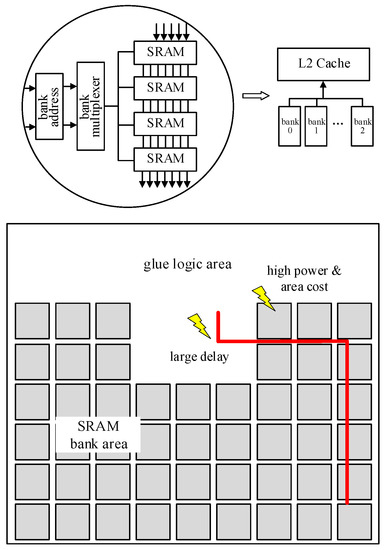

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar

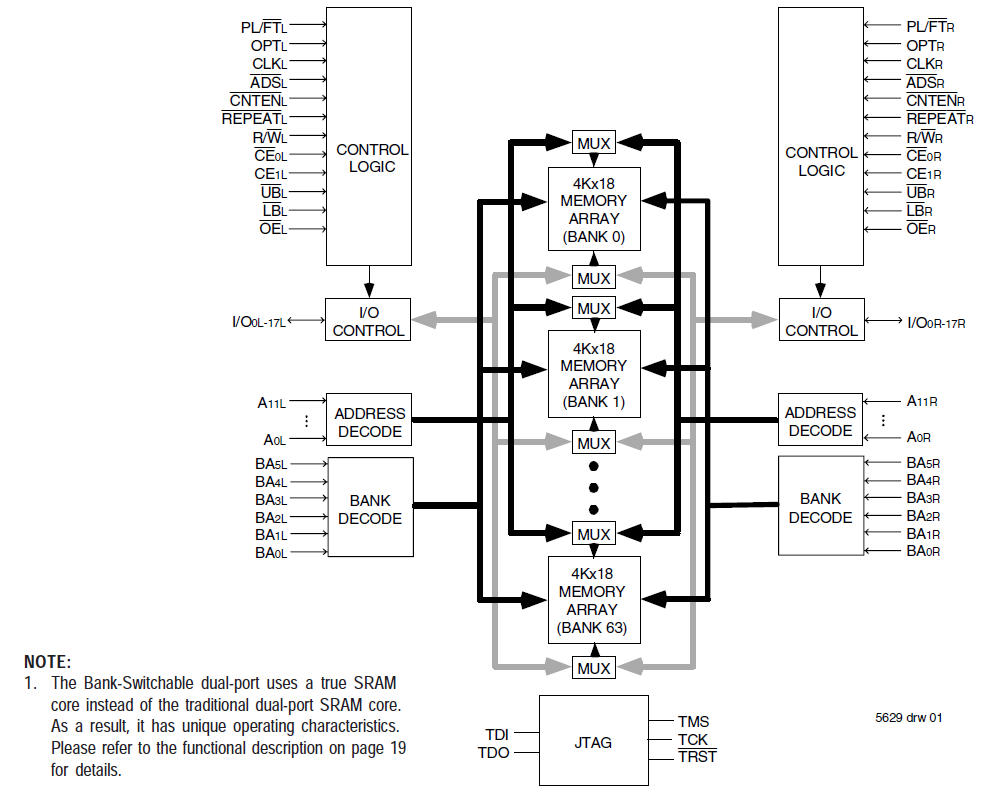

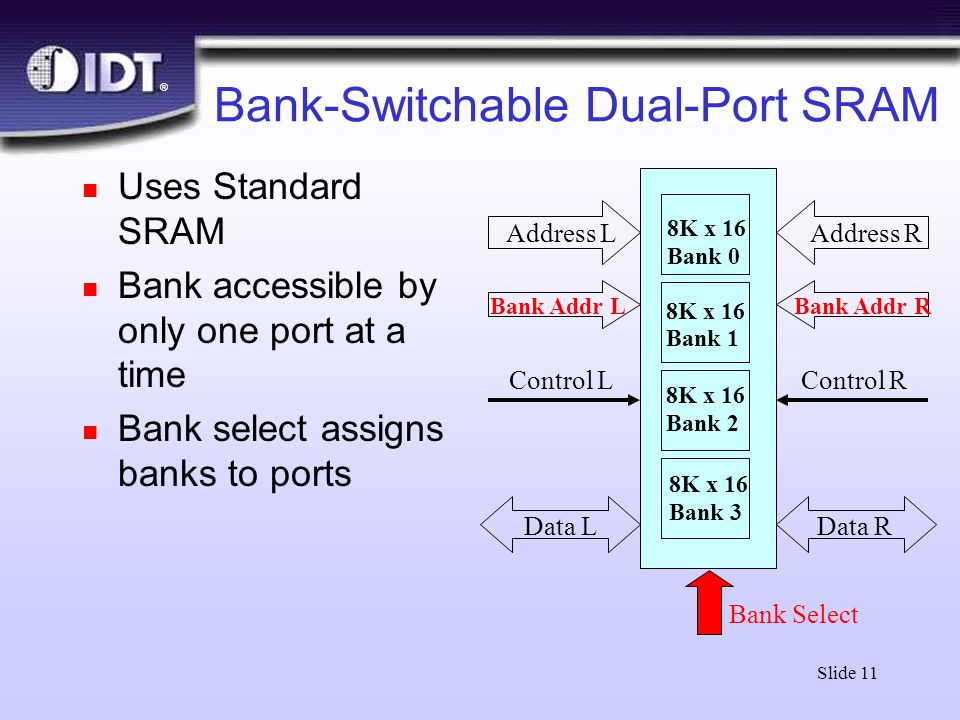

Multi-Port SRAM Overview. ® Slide 2 Objectives n What are Multi-Port SRAMs? n Why are they needed? n Arbitration Features l Busy l Interrupt l Semaphore. - ppt download